SPICEのデバイスモデル〈その3 絶縁ゲート型電界効果トランジスタ〉技術解説

- 高度ポリテクセンター(高度職業能力開発促進センター)山崎 雅博*

*現ポリテクカレッジ群馬

1.はじめに

SPICEのデバイスモデルシリーズは,回路設計シミュレータSPICEを,回路技術者を目指す訓練生等がより有効に使用するために,そこで用いられているモデルに対する必要最小限の基礎事項を解説しています。このため,これらの解説は,電子回路で用いられている素子(特に能動素子)の特性とこれを表現しているSPICEのモデルパラメータとの関連について,素子の動作原理に基づいて述べているものです。

今回は,シリーズの最終回として,ICに最も使用されている絶縁ゲート型電界効果トランジスタ(IGFETもしくはMOSFET)について述べます。

MOSFETは,ゲートに印加する電圧により電流を制御するデバイスで,伝導に寄与するキャリアが電子なのか正孔なのかによってNチャネルとPチャネルの2種類に分けられます。ここでは,電子の移動度が正孔の移動度より数倍大きいことに起因して,動作速度の速いNチャネルMOSFET(N-MOSFET)を取り上げます。またSPICEにおけるMOSFETモデルには,レベル1からレベル3までが存在し,レベルの値が大きくなるほどモデルの精度が向上します。しかし,本シリーズの目的を考慮して,ここでは最も基礎となるレベル1直流モデルに限定して解説します。

2.N-MOSFETについて

2.1 N-MOSFETの構造

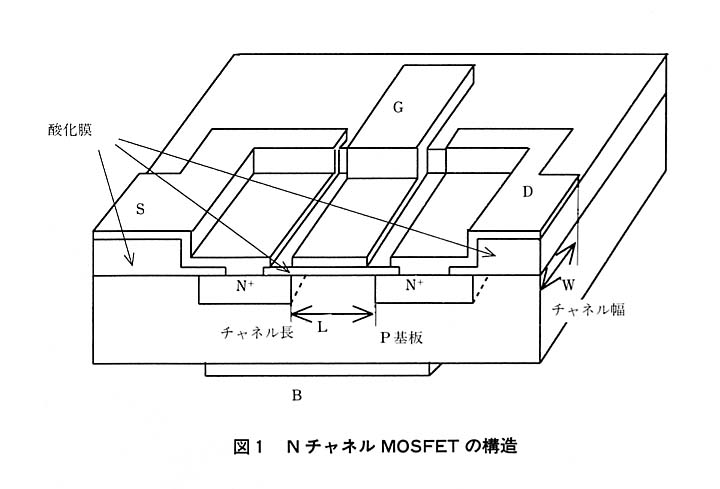

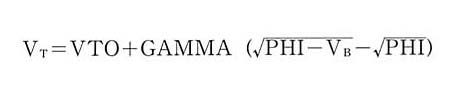

図1に一般的なN-MOSFETの構造図を示します。P形半導体の基板の上に薄い絶縁体の酸化膜が存在し,ゲート電極Gが,金属またはポリシリコンによって作成されています。さらにゲートの両端にあるソース電極Sとドレイン電極Dおよび最下層の基板電極Bから構成されています。このようにN-MOSFETは,4つの電極を有した4極素子です。図中のLは,ソースとドレイン間の距離でチャネル長,Wは,チャネル幅と呼ばれ,これらは,素子が微細化すればするほど小さくなります。

2.2 N-MOSFETの動作原理

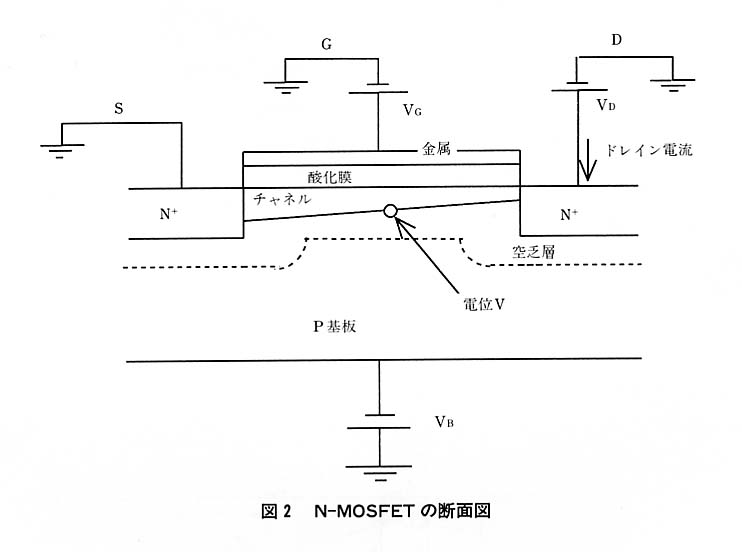

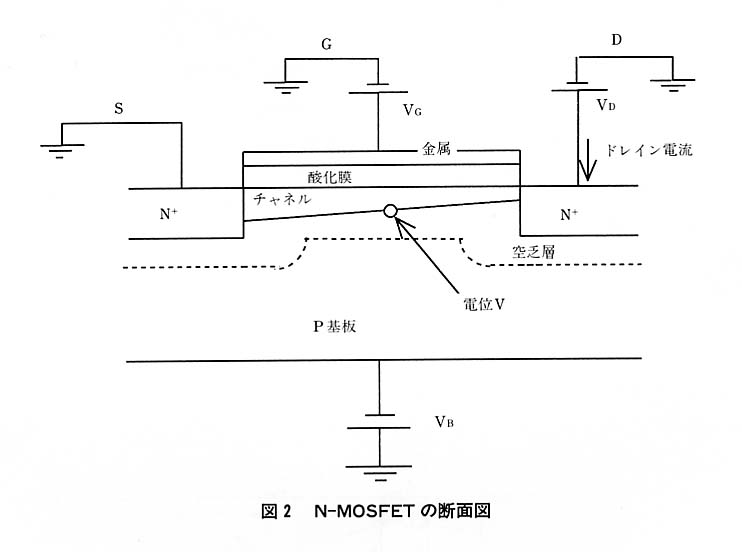

図2にN-MOSFETの断面図を示します。この動作原理は,非常に簡単です。通常N-MOSFETは,図中に示されるようにソースを接地して,ゲートおよびドレインに正の電圧.(VG,VD)を印加して使用されます。つまりソースは,電圧の基準になります。ゲート電圧は,基板のP形半導体の少数キャリア(電子)をゲート付近の半導体表面に蓄積させます。するとソースとドレイン間には,電子の道が生じ,これはチャネルと呼ばれています。ドレイン電圧は,その蓄積された電子を引き寄せるので,チャネルを通じてドレイン電流(ID)を流します。しかしながら,ドレイン電流が流れるためには半導体表面の電子濃度が,そこでの多数キャリア(正孔)濃度より大きくなっていなければなりません。これを反転と呼んでいますが,この反転現象を生じるために,ある程度のゲート電圧が必要になります。この電圧は,しきい値電圧VTと呼ばれています。最後の基板電圧VBには,通常ソースに対して逆バイアス電圧が印加され,このしきい値電圧を変化させる効果を持っています。

2.3 N-MOSFETの物理式

N-MOSFETは,酸化膜を誘電体として,ゲート電極と基板電極を対向電極とする平行平板コンデンサと見なせます。このためゲート電極に印加された電圧VGは,酸化膜と基板表面にかかる電圧(VOX,φS)および接触電位差と酸化膜中の固定電荷を打ち消すために必要な電圧VFB(フラットバンド電圧と呼ばれている)を加えたものになります。したがって酸化膜の単位面積当たりの容量をCOとすると,基板表面に誘起される電荷QSは,

QS=-CO(VG-φS-VFB)

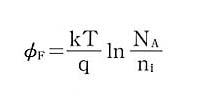

と表されます。ここでMOSFETの動作は,反転現象が起こるまでは意味がありません。そこで図2を参照して,基板表面にかかる電圧は,チャネルに沿った方向でのチャネルの深さ方向端のある点での電圧をVとすると,φS=2φF+Vでなければなりません。ここで2φFは,ドレイン電圧が印加されていないときの反転現象を引き起こすために必要となる表面電位を表しています。なおφFは,フェルミポテンシャルと呼ばれ,基板の不純物濃度をNA,その真性キャリア濃度をni,素電荷をq,ボルツマン定数をk,絶対温度をTとすると,

という値を持つものです。

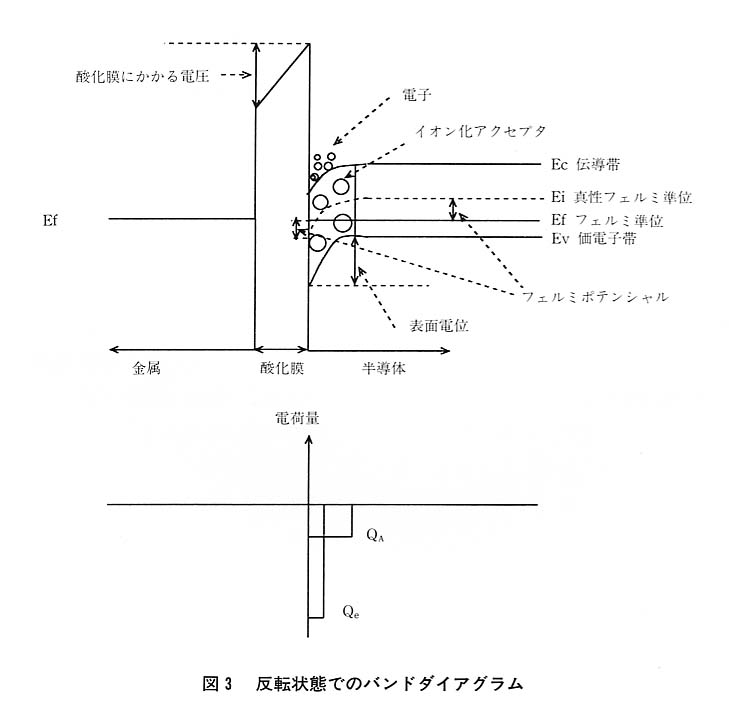

次に基板表面の電荷は,図3の反転状態下でのバンドダイアグラムに示されているように,空乏層中の固定電荷(イオン化アクセプタQA)と反転層の電荷(電子Qe)の和となっています。

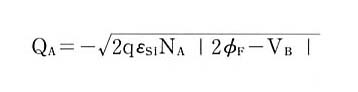

この空乏層中の固定電荷は,基板に逆バイアス状態で印加されている基板電圧VBを考慮すると,

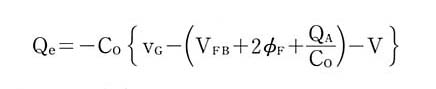

で表されます。ここで,εSiは,基板の誘電率です。以上より反転層中の電荷は,

と求められます。

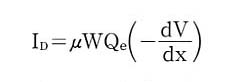

この反転層中の電荷が,流れるドレイン電流の大きさを決定します。つまり電子の基板表面での移動度をμ,チャネル幅をW,チャネル方向をxとすると,ドレイン電流は,

より求められます。また,

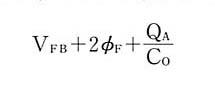

は,反転状態を作り出すのに必要なゲート電圧(しきい値電圧VT)を表しています。以上のことから,反転層中の電荷によって流れるドレイン電流は,接地されたソース電極をx方向の基準にして,チャネル長0~Lまで,電圧は,ソース電圧0からチャネル終端のドレイン電圧VDまで積分することにより,

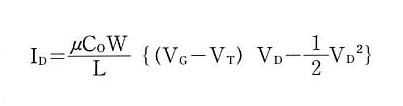

と求められます。

これからドレイン電圧の小さい範囲において,ドレイン電圧に比例したドレイン電流が流れることになり,この特性を持った領域は,線形領域と呼ばれています。

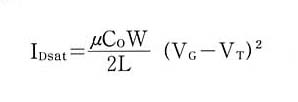

また,ドレイン電圧がVG-VT以上になると,上式はドレイン電圧に無関係になり,ドレイン電流は,ゲート電圧に依存したある値,

で飽和します。この特性領域は,飽和領域と呼ばれています。

3.MOSFETモデルとパラメータについて

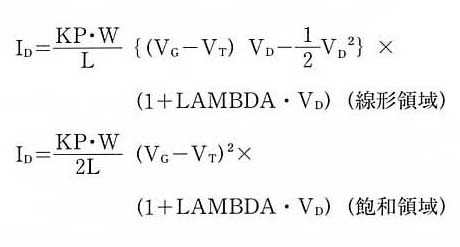

MOSFETモデルは,ドレイン電流の物理式に,ドレイン電圧の増加に伴い実効的なチャネル長が短くなる短チャネル効果を,パラメータLAMBDAによって近似表現した次式を使用しています。

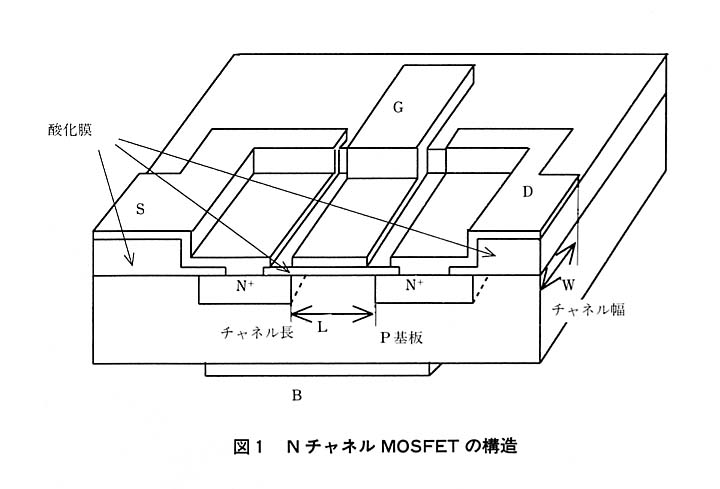

ここで,しきい値電圧VTは,基板電圧VBが0のときのしきい値電圧パラメータVTOおよびフェルミポテンシャルの2倍の2φFという値の表面電位を表すパラメータPHIに,GAMMAというパラメータを用いて基板電圧の効果を取り入れた,

より計算されます。KPは,トランスコンダクタンスを表しているパラメータでキャリアの表面移動度と酸化膜容量の積を表す値です。L,Wは,図1より明らかなように,チャネル長,チャネル幅を表すパラメータです。

これらの電気的パラメータKP,PHI,GAMMAの値を指定する代わりに,以下のプロセスパラメータや物理的パラメータを用いることも可能です。これらは,酸化膜厚を表すプロセスパラメータTOX,表面移動度を表す物理的パラメータUO,基板の不純物濃度を表すプロセスパラメータNSUBです。これらは,SPICEのデバイス方程式プログラム中のヘッダファイルで定義されている誘電率(EPSOXおよびEPSO),電気素量(CHARGE),誘電率(EPSSIL),ボルツマン定数(BOLTZ)とともに用いられることによって,計算式から電気的パラメータの値が求められるという仕組みになっています。

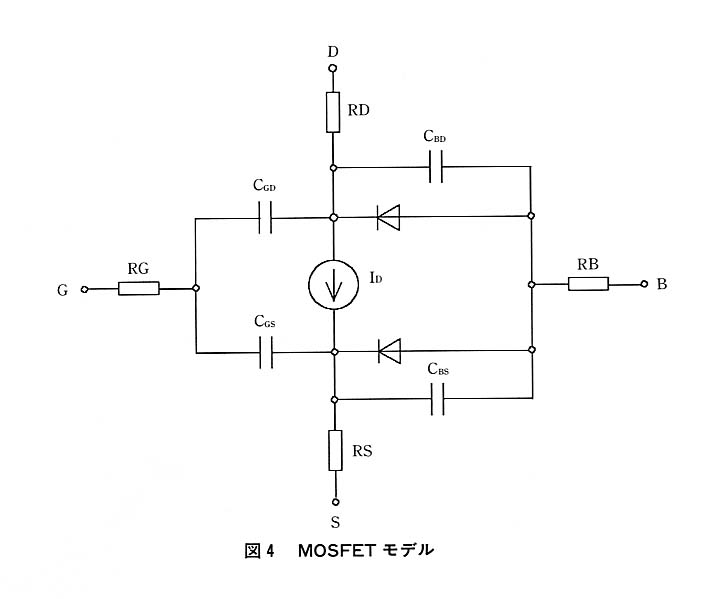

次にゲート電極下の酸化膜容量CO以外にソース,ドレインと基板間のそれぞれのPN接合(ダイオード)による接合容量とそこを流れるダイオードの飽和電流のモデル化がなされています。これらは,基本的にダイオード編で述べられたモデル式と同じですが,接合容量においてやや異なっています。接合容量は,ソース,ドレインの拡散層の面積(パラメータAS,AD)に関わる容量と,拡散層の周囲長(パラメータPS,PD)に関わる容量に分割され,これらの和が,ソース・基板間,ドレイン・基板間のそれぞれの接合容量となっています。このため,単位面積当たりの容量を表すパラメータCJと単位長当たりの容量を表すパラメータCJSW,および拡散層の面領域での接合傾斜係数パラメータMJと拡散層周囲の線領域での接合傾斜係数パラメータMJSWが導入されています。そして,これらのパラメータとPN接合の拡散電位差を表すパラメータPBから各接合容量を計算で決定しています。ここでも上記のパラメータの代わりにソース・基板間接合容量パラメータCBS,ドレイン・基板間接合容量パラメータをCBDを用いて,これらの値を直接決定してもかまいません。

最後に,ソース,ドレイン,ゲートおよび基板の寄生抵抗のモデル化がなされています。これらは,拡散層のシート抵抗を表すパラメータRSHとソース,ドレイン,ゲートおよび基板の矩形数を表すパラメータNRS,NRD,NRG,NRBの積で求められます。また,これらのパラメータの代わりに直接ソース,ドレイン,ゲート,基板の寄生抵抗を表すパラメータRS,RD,RG,RBの値を決定することも可能になっています。

以上のことを考慮して,SPICEでのMOSFETのモデルは,図4のようになっています。この図でCGS,CGDは,ゲート電極下の酸化膜容量値がソース側とドレイン側に分割されたものです。

4.おわりに

今回述べたMOSFETモデルは,Shichman-Hodgesによる最も粗い近似下でのモデルです。この精度を向上させるために,多くの人々によって改善がなされています。これらの中でFrohman-Bentehkowskyによる飽和領域での有限コンダクタンスと移動度の表面電界依存性を考慮したモデル,Hoeheisenによるキャリアの速度飽和現象を表現したモデル,Yauによる短チャネル効果を表現したモデル等は有名です。現在においても,いろいろなモデルが提案されていますが,これらの新しいモデルは,C言語で書かれたデバイス方程式プログラムに新しい計算式(パラメータ)を追加することによってSPICEに組み込むことが可能です。

今後,訓練生等のユーザが,半導体の物理現象についての研究・開発を重ねることによって自作した新しいモデルをSPICEに組み込んで,より実際に近いシミュレーションが実施されることを期待しています。

〈参考文献〉

- 1) Semiconductor Device Modeling with SPICE,McGRAW-HILL

- 2) MicroSim:PSpice 取扱い説明書,Ver.4.05,MicroSim Co.,1991.